STM32F2XX тактирование

Пример разгона STM32F205RB до 120МГц с внешнего кварца на 8МГц и 25МГц (tutorial) Проверено на STM32F205RBT6, должно работать на STM32F207, STM32F215, STM32F217.

RCC->CR |= ((uint32_t)RCC_CR_HSEON);

// Ожидаем готовности HSE

while((RCC->CR & RCC_CR_HSERDY) == 0){;}

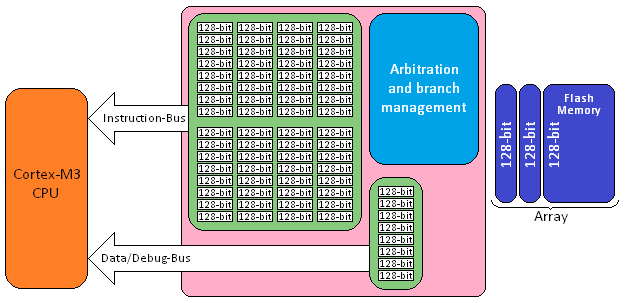

Теперь нужно настроить FLASH память, для этого нужно включить буфер предвыборки, и установить 3 цикла ожидания. В STM32F2xx есть такая интересная штука как ART - акселератор. Он позволяет компенсировать медленную скорость флешки, выбирая на несколько шагов нужные инструкции и данные, его мы тоже включим.

FLASH->ACR = FLASH_ACR_PRFTEN | FLASH_ACR_ICEN | FLASH_ACR_DCEN | FLASH_ACR_LATENCY_3WS;

Рис. 2. Структура ART-акселератора

4. Вся периферия в Cortex-m3 весит на специальных шинах Advanced High-performance Bus (AHB) / Advanced Peripheral Bus (APB). В STM32F2xx AHB, APB1, и APB2.

Шины имеют свою максимальную частоту, AHB может работать на максимальной частоте ядра до 120МГц,

APB1 - 30мгц и APB2 - 60МГц. Поэтому нужно установить предделители AHB /1, APB1 /4, APB2 /2.

RCC->CFGR |= RCC_CFGR_HPRE_DIV1;

RCC->CFGR |= RCC_CFGR_PPRE2_DIV2;

RCC->CFGR |= RCC_CFGR_PPRE1_DIV4;

Так мы подготовили FLASH и шины процессора к высокой частоте и включили внешний кварц.

Частота кварца может быть между 4 и 26 МГц. На крисcтале STM32FXX есть встроенный умножитель частоты с ФАПЧ (PLL).

Он позволяет получить широкий спектр частот для тактированния контроллера. Перед тем как его включить нужно его настроить.

Это самое сложное, при настройке PLL необходимо учитывать что мы хотим получить на его выходе.

Формула для расчетов PLLCLK = ((HSE / PLL_M) * PLL_N) / PLL_P, где PLLCLK — частота на выходе PLL, она же и попадает на процессор.

HSE — частота кварцевого генератора (задается внешним кварцом), PLL_M — фактор деления PLL принимает значения 2 - 63,

PLL_N — фактор умножения PLL принимает значения 64 - 432. Есть правило, результат (HSE / PLL_M) * PLL_N должен быть в приделах 64 - 432,

PLL_P — предделитель основного тактового сигнала после PLL. Пример конфигурации PLL для получения частоты 120мгц с кварцом на 8 и на 25МГц

Расчеты:

PLLCLK = ((HSE(8) / PLL_M(8)) * PLL_N(240)) / PLL_P(2) = 120 (8 мГц)

PLLCLK = ((HSE(25) / PLL_M(25)) * PLL_N(240)) / PLL_P(2) = 120 (25 мГц)

Теперь у нас системная частота будет равна 120 МГц, осталось позаботиться про USB, SDIO и генератор случайных чисел, им для нормальной работы нужно 48 МГц.

PLL_Q задает коэффициент деления системной частоты для этих устройств. PLL_Q принимает значения 2 - 15, а для частоты PLL 240 МГц - 5 (240 / 5 = 48).

RCC->PLLCFGR = PLL_M | (PLL_N << 6) |

(((PLL_P >> 1) -1) << 16) |

(RCC_PLLCFGR_PLLSRC_HSE) |

(PLL_Q << 24);

RCC->PLLCFGR = 8 | (240 << 6) |

(((2 >> 1) -1) << 16) |

(RCC_PLLCFGR_PLLSRC_HSE) |

(5 << 24);

RCC->PLLCFGR = 25 | (240 << 6) |

(((2 >> 1) -1) << 16) |

(RCC_PLLCFGR_PLLSRC_HSE) |

(5 << 24);

Конфигурирование закончено.

RCC->CR |= RCC_CR_PLLON;

// Ожидаем запуска PLL:

while((RCC->CR & RCC_CR_PLLRDY) == 0){;}

// Выбираем источником тактового сигнала генератор PLL:

RCC->CFGR |= RCC_CFGR_SW_PLL;

//Ждем когда контроллер перейдет на тактирование от PLL:

while ((RCC->CFGR & RCC_CFGR_SWS) != RCC_CFGR_SWS_PLL){;}